# PhD Thesis

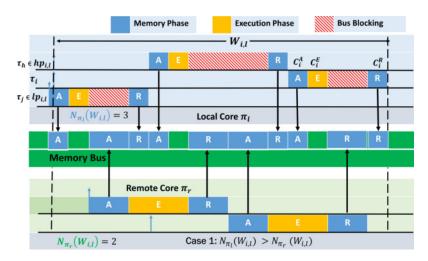

### Shared Resource Contention-Aware Schedulability Analysis of Hard Real-Time Systems

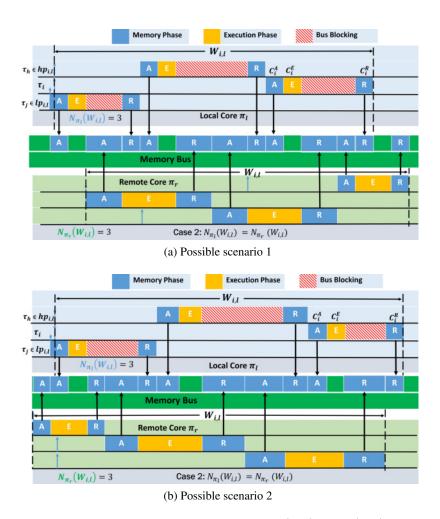

The PhD examination committee was composed of:

President: Prof. José Nuno Moura Marques Fidalgo, Associate Professor at the Faculty of Engineering of the University of Porto, Portugal;

Referee: Prof. Renato Mancuso, Assistant Professor in the Department of Computer Science at Boston University, USA;

Referee: Prof. Isabelle Puaut, Full Professor at the University of Rennes, France;

Referee: Prof. Pedro Alexandre Guimarães Lobo Ferreira Souto, Assistant Professor at the Faculty of Engineering of the University of Porto, Portugal;

Supervisor: Prof. Eduardo Manuel Medicis Tovar, Director of the CISTER

### **Jatin Arora**

CISTER-TR-231001

2023/09/08

# Shared Resource Contention-Aware Schedulability Analysis of Hard Real-Time Systems

#### Jatin Arora

CISTER Research Centre Polytechnic Institute of Porto (ISEP P.Porto) Rua Dr. António Bernardino de Almeida, 431 4200-072 Porto Portugal Tel.: +351.22.8340509, Fax: +351.22.8321159 E-mail: jatin@isep.ipp.pt https://www.cister-labs.pt

#### Abstract

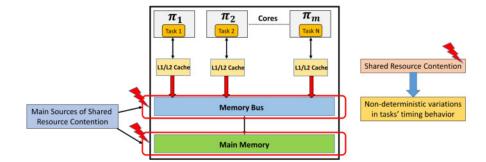

Modern commercial-off-the-shelf (COTS) multicore processors were introduced to provide raw computing power and to build energy-efficient and cost-effective solutions. As a consequence, they have been used in most modern computing systems. However, the adoption of multicore platforms in hard real-time systems, i.e., systems that run applications with stringent time requirements, is still under the scrutiny of the real-time systems research community. One of the main challenges that hinder the use of COTS multicore platforms in hard real-time systems is their unpredictability, which originates from the sharing of different hardware resources such as shared caches, interconnect (e.g., memory bus), and the main memory. Specifically, a task executing on one core of a multicore platform has to compete with other co-running tasks (tasks running on other cores) to access these shared resources. This contention between tasks to access shared resources is formally known as the shared resource contention. Shared resource contention is problematic as it can negatively influence the temporal behavior of tasks in a non-deterministic manner. To safely determine whether all tasks running in the system can execute without violating their respective timing constraints, one of the most important factors is to analyze and derive a safe bound on the maximum shared resource contention that tasks can suffer.

The main objective of this dissertation is to build novel solutions to accurately quantify the shared resource contention that can be suffered by tasks due to the sharing of resources such as the memory bus and the main memory.

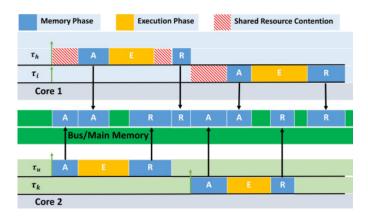

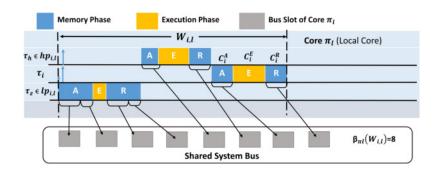

Among all the existing solutions that eliminate/allow analyzing the shared resource contention, the phased execution model has been identified as a good solution that enables a more precise analysis of the shared resource contention. Specifically, the idea of the phased execution model is to divide the task execution into distinct computation and memory phases such that a shared resource, e.g., main memory, can be accessed by the tasks only during their memory phases. However, shared resource contention can still occur even when tasks comply with the phased execution model, e.g., when memory phases of tasks running on different cores execute concurrently.

In this dissertation, we start by modeling and analyzing the maximum memory bus contention, i.e., contention due to the sharing of memory bus that can be suffered by tasks under the phased execution model. We then evaluate the impact of the bus arbitration policy on the bus contention that tasks can suffer by varying the bus arbitration policy. Results show that the use of a fairer bus arbitration scheme along with the phased execution model can lead to a tighter bound on the memory bus contention.

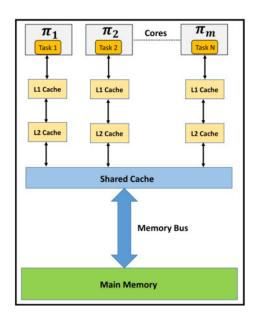

We also investigate the relationship between the memory bus and the cache memories. Specifically, we show that the bus contention strongly relates to the number of bus requests which further depends on the content of cache memories. Building on this, we propose the holistic bus contention analysis that analyzes the cache memories to bound the maximum number of cache misses and integrate them in the computation of the maximum bus contention that phased tasks can suffer.

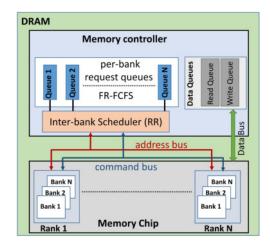

Furthermore, we improve the bounds on the main memory contention of phased tasks considering dynamic random access-based memory systems. We first identify the pessimism in the existing analysis that lies in the overestimation of the memory contention that can be caused by the write memory requests. We then propose a memory contention analysis that accurately quantifies the memory contention that can be suffered by tasks. We also show how the memory address mapping of tasks can impact the maximum memory contention that tasks can suffer.

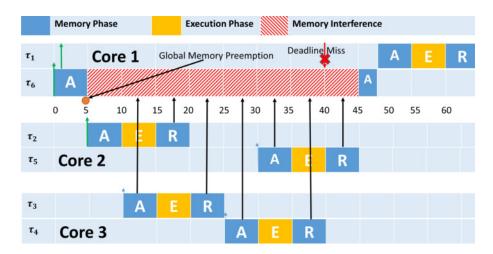

Finally, we focus on the memory-centric scheduling that schedules the memory phases of all tasks running on the system such that multiple tasks cannot access the main memory concurrently to avoid shared resource contention. However, tasks can still be delayed, for example, if the memory scheduler is currently serving a memory phase of a task on another core. We first identify the sources of pessimism in the recent memory-centric scheduling-based analysis. We then provide insights on how such pessimism can be addressed. Building on this, we propose an improved memory-centric scheduling-based analysis that addresses the pessimism of the existing analysis.

Keywords: Real-time systems, Hard real-time systems, Multicore processors, Shared resources, Bus contention, Memory contention, Timing analysis.

FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Shared Resource Contention-Aware Schedulability Analysis of Hard Real-Time Systems

Jatin Arora

Doctoral Program in Electrical and Computer Engineering Supervisor: Prof. Dr. Eduardo Manuel Medicis Tovar Co-Supervisor: Dr. Cláudio Roberto Ribeiro Maia Co-Supervisor: Prof. Dr. Luís Miguel Pinho de Almeida

September 8, 2023

© Jatin Arora: September, 2023

#### Shared Resource Contention-Aware Schedulability Analysis of Hard Real-Time Systems

**Jatin Arora**

Doctoral Program in Electrical and Computer Engineering

Approved by:

President: Prof. José Nuno Moura Marques Fidalgo Referee: Prof. Renato Mancuso Referee: Prof. Isabelle Puaut Referee: Prof. Pedro Alexandre Guimarães Lobo Ferreira Souto Supervisor: Prof. Eduardo Manuel Medicis Tovar

September 8, 2023

Dedicated this special feat to my parents, the most important pillars of my life, who stood by me through every failure and triumph.

ii

## Abstract

Modern commercial-off-the-shelf (COTS) multicore processors were introduced to provide raw computing power and to build energy-efficient and cost-effective solutions. As a consequence, they have been used in most modern computing systems. However, the adoption of multicore platforms in *hard real-time systems*, i.e., systems that run applications with *stringent time require-ments*, is still under the scrutiny of the real-time systems research community. One of the main challenges that hinder the use of COTS multicore platforms in hard real-time systems is their unpredictability, which originates from the *sharing* of different *hardware resources* such as shared caches, interconnect (e.g., memory bus), and the main memory. Specifically, a task executing on one core of a multicore platform has to compete with other co-running tasks (tasks running on other cores) to access these *shared resources*. This contention between tasks to access shared resources is formally known as the *shared resource contention*. Shared resource contention is problematic as it can negatively influence the temporal behavior of tasks in a *non-deterministic manner*. To safely determine whether all tasks running in the system can execute without violating their respective timing constraints, one of the most important factors is to analyze and derive a safe bound on the maximum shared resource contention that tasks can suffer.

The main objective of this dissertation is to build novel solutions to accurately quantify the shared resource contention that can be suffered by tasks due to the sharing of resources such as the memory bus and the main memory.

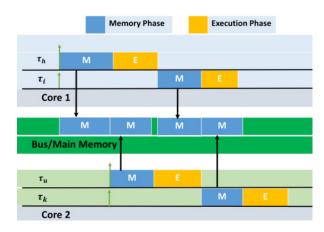

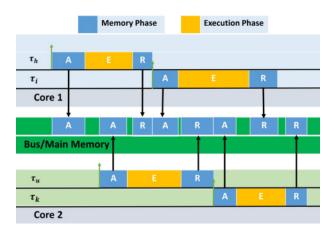

Among all the existing solutions that eliminate/allow analyzing the shared resource contention, the *phased execution model* has been identified as a good solution that enables a more precise analysis of the shared resource contention. Specifically, the idea of the phased execution model is to divide the task execution into distinct *computation* and *memory phases* such that a shared resource, e.g., main memory, can be accessed by the tasks only during their memory phases. However, shared resource contention can still occur even when tasks comply with the phased execution model, e.g., when memory phases of tasks running on different cores execute concurrently.

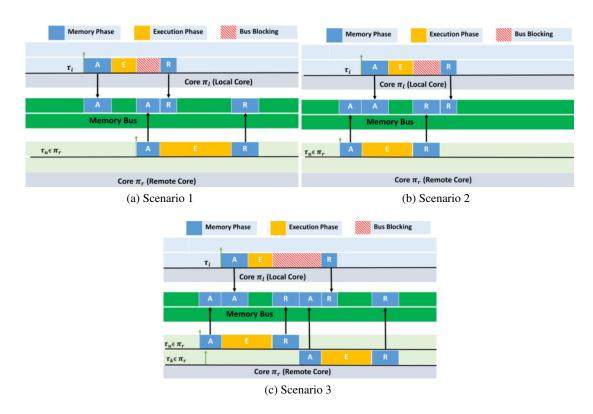

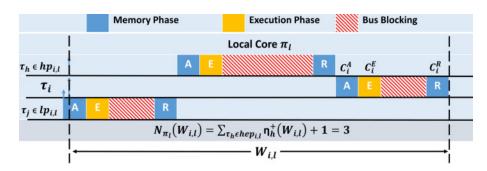

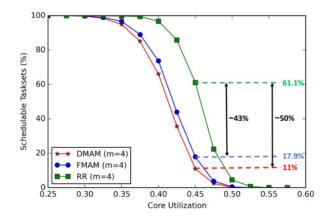

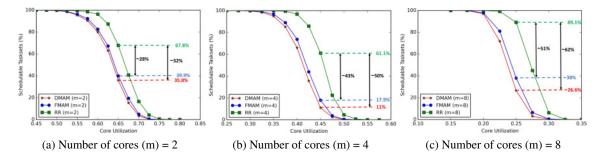

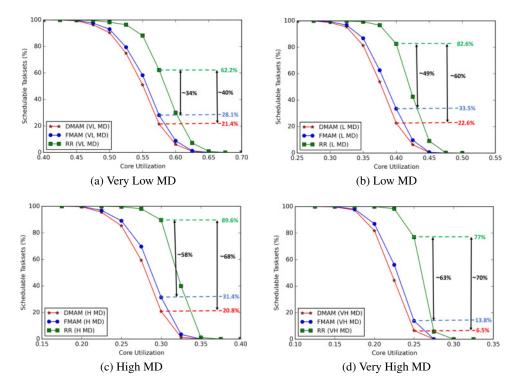

In this dissertation, we start by modeling and analyzing the maximum *memory bus contention*, i.e., contention due to the sharing of *memory bus* that can be suffered by tasks under the phased execution model. We then evaluate the impact of the bus arbitration policy on the bus contention that tasks can suffer by varying the bus arbitration policy. Results show that the use of a fairer bus arbitration scheme along with the phased execution model can lead to a tighter bound on the memory bus contention.

We also investigate the relationship between the memory bus and the cache memories. Specifically, we show that the bus contention strongly relates to the number of bus requests which further depends on the content of cache memories. Building on this, we propose the *holistic bus contention analysis* that analyzes the cache memories to bound the maximum number of *cache misses* and integrate them in the computation of the maximum bus contention that phased tasks can suffer.

Furthermore, we improve the bounds on the *main memory contention* of phased tasks considering dynamic random access-based memory systems. We first identify the pessimism in the existing analysis that lies in the overestimation of the memory contention that can be caused by the write memory requests. We then propose a memory contention analysis that accurately quantifies the memory contention that can be suffered by tasks. We also show how the memory address mapping of tasks can impact the maximum memory contention that tasks can suffer.

Finally, we focus on the *memory-centric scheduling* that schedules the memory phases of all tasks running on the system such that multiple tasks cannot access the main memory concurrently to avoid shared resource contention. However, tasks can still be delayed, for example, if the memory scheduler is currently serving a memory phase of a task on another core. We first identify the sources of pessimism in the recent memory-centric scheduling-based analysis. We then provide insights on how such pessimism can be addressed. Building on this, we propose an improved memory-centric scheduling-based analysis that addresses the pessimism of the existing analysis.

**Keywords:** Real-time systems, Hard real-time systems, Multicore processors, Shared resources, Bus contention, Memory contention, Timing analysis.

### Resumo

Processadores multinúcleo comercialmente disponíveis foram introduzidos para fornecer maior poder de computação e para criar soluções económicas e eficientes em termos de energia. Como consequência, eles têm sido usados na maioria dos sistemas de computação modernos. No entanto, a adoção de plataformas multinúcleo em sistemas de tempo real rígidos, ou seja, sistemas que executam aplicações com requisitos de tempo rigorosos, continuam a ser tema de investigação atual da comunidade de sistemas de tempo real. O principal desafio que dificulta o uso destes processadores multinúcleo em sistemas de tempo real rígido é sua imprevisibilidade, que se origina no uso partilhado de diferentes recursos de hardware, como memórias cache, interconexão (por exemplo, barramento de memória) e memória principal. Mais especificamente, uma tarefa executada num núcleo de uma plataforma multinúcleo precisa competir com outras tarefas co-executadas (tarefas executadas em outros núcleos) para aceder a estes recursos compartilhados. Essa disputa entre tarefas para aceder aos recursos compartilhados é formalmente conhecida como contenção de recurso compartilhado. A contenção de recursos compartilhados é problemática, pois pode influir negativamente o comportamento temporal das tarefas de maneira não determinística. Para determinar com segurança se todas as tarefas em execução no sistema podem ser executadas sem violar as suas respetivas restrições de tempo, é necessário analisar a contenção máxima de recursos compartilhados que as tarefas podem sofrer.

O principal objetivo desta dissertação é desenvolver novas soluções para, com precisão, quantificar o impacto que a contenção de recursos partilhados, como o barramento de memória e a memória principal, tem na execução de tarefas.

Dentre todas as soluções existentes que eliminam/permitem analisar a contenção de recursos compartilhados, o modelo de execução em fases tem sido identificado como uma solução promissora que possibilita uma análise mais precisa deste tipo de contenção. Mais especificamente, a ideia do modelo de execução em fases é dividir a execução da tarefa em distintas fases de execução e de acesso à memória, de modo que um recurso compartilhado, por exemplo, memória principal, possa ser acedido pelas tarefas apenas durante as suas fases de acesso à memória. No entanto, a contenção de recursos compartilhados ainda assim pode ocorrer mesmo quando as tarefas obedecem ao modelo de execução em fases, por exemplo, quando as fases de memória de tarefas executadas em diferentes núcleos são executadas simultaneamente.

Neste trabalho, começamos por modelar e analisar a contenção máxima do barramento de memória, ou seja, o atraso devido à partilha do barramento de memória que pode ser sofrido por tarefas sob o modelo de execução em fases. Em seguida, avaliamos o impacto sofrido pelas tarefas ao aplicarmos variações da política de arbitragem do barramento. Os resultados mostram que o uso de um esquema de arbitragem de barramento mais justo em conjunto com o modelo de execução em fases pode levar a um limite com menos variações na contenção do barramento de memória.

Também investigamos a relação entre o barramento de memória e as memórias cache. Especificamente, mostramos que a contenção do barramento está fortemente relacionada ao número de requisições de barramento, que depende ainda mais do conteúdo das memórias cache. Com base nisso, propomos a análise holística de contenção de barramento que analisa as memórias cache para limitar o número máximo de faltas de cache e integrá-las no cálculo da contenção máxima de barramento que as tarefas em fases podem sofrer.

Além disso, melhoramos os limites da contenção de memória principal de tarefas em fases considerando sistemas de memória dinâmicos baseados em acesso aleatório. Primeiro identificamos o pessimismo na análise existente que reside na superestimação da contenção de memória que pode ser causada pelas solicitações de escrita de memória. Em seguida, propomos uma análise de contenção de memória que quantifica, com precisão, a contenção de memória que as tarefas podem sofrer. Também mostramos como o mapeamento do endereço de memória das tarefas pode impactar na contenção máxima de memória sofridas pelas tarefas.

Por fim, focamos no escalonamento centrado na memória que escalona as fases de memória de todas as tarefas em execução no sistema de forma que duas tarefas não acedam a memória principal simultaneamente para evitar a contenção de recursos compartilhados. No entanto, as tarefas ainda podem ser atrasadas, por exemplo, se o escalonador de memória estiver a atender a uma fase de memória de uma tarefa em outro núcleo. Primeiro identificamos as fontes de pessimismo na recente análise baseada em escalonamento centrada na memória. Em seguida, fornecemos intuições sobre como esse pessimismo pode ser abordado. Com base nisso, propomos uma análise aprimorada baseada em agendamento centrado na memória que aborda o pessimismo existente na análise.

Palavras-chave: Sistemas de tempo real, Sistemas de tempo real rígido, Processadores multinúcleo, Recursos partilhados, Contenção de barramento, Contenção de memória, Análise temporal

## Acknowledgments

The roller coaster journey of PhD research would not be completed without the support of different individuals. First and foremost, I would like to express my heartfelt gratitude to my supervisor, **Prof. Eduardo Tovar**, for his unwavering support throughout my PhD journey. I am truly grateful to him for consistently encouraging my proactive approach toward research and participation in various activities. Being the director of CISTER, he also ensured excellent hosting conditions.

I also extend my sincere appreciation to my co-supervisor, **Dr. Cláudio Maia**, for his invaluable support and thorough review of the majority of the work conducted during my PhD studies. His expertise has provided crucial feedback from both analytical and practical perspectives, which helped me in carrying out the research work presented in this dissertation.

I am immensely grateful to **Dr. Syed Aftab Rashid** for his invaluable feedback on most of the work developed during my PhD studies. I had the privilege of collaborating with him during the third year of my PhD. Due to his excellent & timely feedback, we collaborated on almost all works. In fact, he is the main person who helped me for the past one year. Among others, his expert advice on efficiently writing manuscripts and poster preparation was extremely useful.

Furthermore, I would like to express my sincere gratitude to **Dr. Geoffrey Nelissen** for first supervising me in the early stage of PhD and later continuing to collaborate with us after moving to TU/e, Eindhoven. I am especially grateful to him for introducing me to the relevant research problems which helped me in identifying the potential path for my PhD research.

Thanks to **Prof. Luis Almeida** for reviewing this dissertation and for helping with FEUP's administration. Thanks to my dear friend **Giann Nandi** for translating the abstract into Portuguese. Special thanks to the Jury members for their time and efforts in the evaluation of this dissertation.

I am thankful to all the colleagues/friends at **CISTER** for their friendship and good times, especially to David, Giann, Konstantinos, Yilian, Javier, Harrison, Jingjing, Ishfaq, Miguel, Gowhar, Enio, Radha, José, Lukas, Shashank, Mubarak, Patrick, Yousef, Ali, Reydel, Saeid, Luis Javier, Abdul, Shardul, Pedro Santos, Ramiro, Filipe, Alam, Yimin, and Mohammad. I would also like to thank Sandra, Cristiana, Marwin, Inês, and Benilde for their invaluable administrative support.

Most importantly, I want to express my deepest appreciation to my family members for their unwavering love and support. I am especially grateful to my parents, **Mr. Raj Kumar** and **Mrs. Darshana Rani**, for their love, support, and guidance that have profoundly shaped both my personal and professional life. I am also thankful to my siblings/cousins for their love and support, particularly my elder brother **Sumit Arora** who has been the biggest source of inspiration for me. It would have been impossible to achieve this feat without their love, support, and motivation.

Special thanks to all my Indian friends, especially the "Brown Munde Squad", i.e., Pankaj, Sachin, Gaurish and Satinder, for always being the best, most reliable, and funniest friends.

This work was partially supported by FCT (Fundação para a Ciência e Tecnologia) under the individual doctoral grant 2020.09532.BD.

viii

## **List of Publications**

The following list of publications reflects the results achieved during the development of this dissertation.

#### **Journal Publications**

- Jatin Arora, Cláudio Maia, Syed Aftab Rashid, Geoffrey Nelissen, and Eduardo Tovar, "Schedulability Analysis for 3-Phase Tasks with Partitioned Fixed-Priority Scheduling" in Journal of Systems Architecture 131 (2022), 102706. DOI: doi.org/10.1016/j.sysarc.2022.102706

- Jatin Arora, Cláudio Maia, Syed Aftab Rashid, Geoffrey Nelissen, and Eduardo Tovar, "Bus-Contention Aware WCRT Analysis for the 3-Phase Task Model Considering a Work-Conserving Bus Arbitration Scheme" in Journal of Systems Architecture 122 (2022), 102345. (Best Paper Award at ICESS 2021) DOI: doi.org/10.1016/j.sysarc.2021.102345

- Jatin Arora, Syed Aftab Rashid, Geoffrey Nelissen, Cláudio Maia, and Eduardo Tovar, "Memory Contention-aware WCRT Analysis for the 3-Phase Task Model" in ACM Transactions on Embedded Computing Systems (under review).

#### **Conference Publications**

- Jatin Arora, Syed Aftab Rashid, Geoffrey Nelissen, Cláudio Maia, and Eduardo Tovar, "Improved Bus Contention Analysis for 3-Phase Tasks" in 29th IEEE **RTCSA**, Niigata, Japan, 2023. To appear.

- Jatin Arora, Syed Aftab Rashid, Cláudio Maia, Geoffrey Nelissen, and Eduardo Tovar, "Work-in-Progress: A Holistic Approach to WCRT Analysis for Multicore Systems", in 43rd IEEE **RTSS**, Houston, TX, USA, 2022, pp. 511-514, doi: 10.1109/RTSS55097.2022.00054.

- Jatin Arora, Syed Aftab Rashid, Cláudio Maia, and Eduardo Tovar, "Analyzing Fixed Task Priority based Memory Centric Scheduler for the 3-Phase Task Model", in 28th IEEE RTCSA, Taipei, Taiwan, 2022, pp. 51-60, doi: 10.1109/RTCSA55878.2022.00012.

- Jatin Arora, Cláudio Maia, Syed Aftab Rashid, Geoffrey Nelissen, and Eduardo Tovar, "Bus-Contention Aware Schedulability Analysis for the 3-Phase Task Model with Partitioned Scheduling" in 29th **RTNS**, 2021, pp. 123–133, doi.org/10.1145/3453417.3453433.

- Jatin Arora, Cláudio Maia, Syed Aftab Rashid, Geoffrey Nelissen, and Eduardo Tovar, "Work-in-Progress: WCRT Analysis for the 3-Phase Task Model in Partitioned Scheduling," in 41st IEEE RTSS, 2020, pp. 407-410, doi: 10.1109/RTSS49844.2020.00050.

#### **Workshop Publications**

- Jatin Arora, Syed Aftab Rashid, Geoffrey Nelissen, Cláudio Maia, and Eduardo Tovar, "Memory Contention Analysis for 3-Phase Tasks" in JRWRTC, 2023, co-located with RTNS 2023. http://rtns2023-jrwrtc-memory-contention-analysis-for-3-phase-tasks.pdf.

- Jatin Arora, Cláudio Maia, and Syed Aftab Rashid, "Open Questions for the Bus-Blocking Problem in the 3-Phase Task Model under Partitioned Scheduling" in the CAPITAL Workshop, 2021. http://cister-labs.pt/docs/CAPITAL-Workshop-2021.pdf.

#### **PhD Forum and Extended Abstracts**

- Jatin Arora, Eduardo Tovar, and Cláudio Maia, "Shared Resource Contention Aware Schedulability Analysis for Multiprocessor Real-Time Systems" in the PhD Forum, DATE, 2023 (PhD Forum Best Poster Prize). http://cister-labs.pt/docs/DATE-PhD-forum-2023.pdf.

- Jatin Arora, Cláudio Maia, Syed Aftab Rashid, and Eduardo Tovar, "Open Issues in Analyzing the Schedulability for the 3-Phase Task Model using Partitioned Scheduling" in the symposium of Electrical and Computer Engineering of DCE, 2021 doi: doi.org/10.24840/978-972-752-276-7.

#### **Other Publications**

• Jatin Arora, and Patrick Meumeu Yomsi, "Wearable Sensors Based Remote Patient Monitoring using IoT and Data Analytics" in U.Porto Journal of Engineering, Volume 5, Issue 1, pp 34-45, 2019. DOI: doi.org/10.24840/2183-6493-005.001-0003

## Contents

| 1      | Intr               | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                     |

|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|        | 1.1                | Multicore Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                     |

|        | 1.2                | Phased Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                     |

|        | 1.3                | Shared Resource Contention and the 3-Phase Task Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                     |

|        | 1.4                | Thesis Scope and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                     |

|        | 1.5                | Thesis Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                    |

| 2      | Bacl               | kground and Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                    |

|        | 2.1                | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                    |

|        |                    | 2.1.1 Task Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14                                                                    |

|        |                    | 2.1.2 Task Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                    |

|        |                    | 2.1.3 Worst-Case Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                    |

|        |                    | 2.1.4 Hardware Platform Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                    |

|        |                    | 2.1.5 Phased Execution Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                    |

|        | 2.2                | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                    |

|        |                    | 2.2.1 Related Work for the Generic Task Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                                                    |

|        |                    | 2.2.2 Related Work for the Phased Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35                                                                    |

|        | 2.3                | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                    |

|        |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |

| I      |                    | s Contention Analysis for the 3-Phase Task Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                    |

| I<br>3 | Bus                | Contention-Aware Schedulability Analysis for the 3-Phase Task Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                    |

|        |                    | Contention-Aware Schedulability Analysis for the 3-Phase Task Model System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>43</b><br>44                                                       |

|        | Bus                | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model       3.1.1         Task Model       3.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>43</b><br>44<br>44                                                 |

|        | Bus                | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>44<br>45                                           |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>44<br>45<br>46                                     |

|        | Bus                | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47                                     |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47                               |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49                         |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49<br>51                   |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49                         |

|        | <b>Bus</b> 3.1     | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model       3.1.1         Task Model       3.1.2         Streecution Model       3.1.2         Subscript Analysis for the Dedicated Memory Access Model (DMAM)       3.1.3         Bus Blocking Analysis for the Dedicated Memory Access Model (DMAM)       3.2.1         Properties of the DMAM       3.2.2         Bounding the Number of Bus Blockings for the DMAM       3.2.3         Aaximum Bus Blocking Computation for the DMAM       3.2.4         Bus Contention Analysis for all Remote Cores       Bus Blocking Analysis for the Fair Memory Access Model (FMAM) | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49<br>51                   |

|        | <b>Bus</b> 3.1 3.2 | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49<br>51<br>56             |

|        | <b>Bus</b> 3.1 3.2 | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model       3.1.1         Task Model       3.1.2         Streecution Model       3.1.2         Subscript Analysis for the Dedicated Memory Access Model (DMAM)       3.1.3         Bus Blocking Analysis for the Dedicated Memory Access Model (DMAM)       3.2.1         Properties of the DMAM       3.2.2         Bounding the Number of Bus Blockings for the DMAM       3.2.3         Aaximum Bus Blocking Computation for the DMAM       3.2.4         Bus Contention Analysis for all Remote Cores       Bus Blocking Analysis for the Fair Memory Access Model (FMAM) | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49<br>51<br>56<br>57       |

|        | <b>Bus</b> 3.1 3.2 | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b><br>44<br>45<br>46<br>47<br>47<br>49<br>51<br>56<br>57<br>58 |

|        | <b>Bus</b> 3.1 3.2 | Contention-Aware Schedulability Analysis for the 3-Phase Task Model         System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>43</b> 44 44 45 46 47 47 49 51 56 57 58 60                         |

|         |                                               | 3.5.1 Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67                                                                                                                                                                                                            |

|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                               | 3.5.2 Experiments using Synthetic Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71                                                                                                                                                                                                            |

|         | 3.6                                           | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                                                                                                                                            |

| 4       | Fval                                          | luating the Impact of Bus Arbitration Policy on Bus Contention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                                                                                                                                                                            |

| -       | 4.1                                           | System Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78                                                                                                                                                                                                            |

|         |                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                                                                                                                                                                            |

|         |                                               | 4.1.2 Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                                                                                                                                                                            |

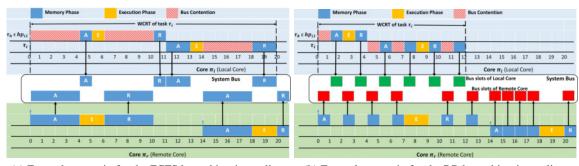

|         | 4.2                                           | Motivational Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                                                                                                                                                                            |

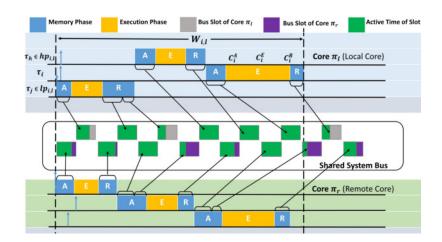

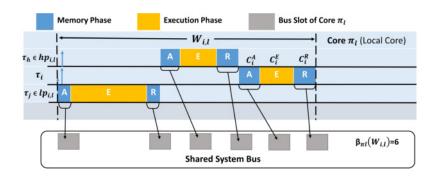

|         | 4.3                                           | Bus Contention Analysis for RR-based Bus Arbitration Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                                                                                                                                                                            |

|         |                                               | 4.3.1 Step 1: Bounding the Maximum Number of Bus Slots required by the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                               |

|         |                                               | Local/Remote Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80                                                                                                                                                                                                            |

|         |                                               | 4.3.2 Step 2: Bounding Maximum Bus Contention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82                                                                                                                                                                                                            |

|         | 4.4                                           | Accurately Estimating the Impact of Lower Priority Blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86                                                                                                                                                                                                            |

|         | 4.5                                           | Schedulability Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89                                                                                                                                                                                                            |

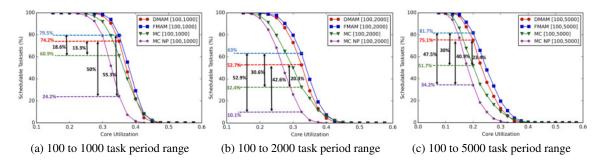

|         | 4.6                                           | Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90                                                                                                                                                                                                            |

|         | 4.7                                           | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95                                                                                                                                                                                                            |

| 5       | Cool                                          | he-aware Bus Contention Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                                                                                                                                                            |

| 3       | 5.1                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98                                                                                                                                                                                                            |

|         | 5.2                                           | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90<br>99                                                                                                                                                                                                      |

|         | 5.3                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100                                                                                                                                                                                                           |

|         | 5.5                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101                                                                                                                                                                                                           |

|         |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 103                                                                                                                                                                                                           |

|         | 5.4                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 104                                                                                                                                                                                                           |

|         | 011                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104                                                                                                                                                                                                           |

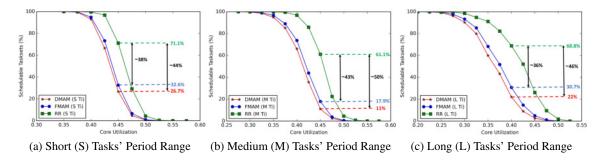

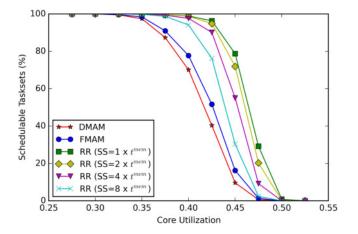

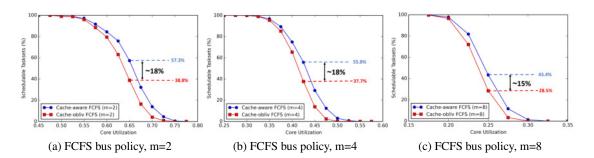

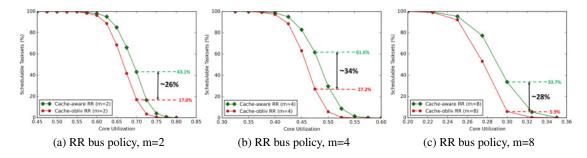

|         |                                               | 5.4.2 Cache-aware Bus Contention Analysis for the FCFS Bus Arbitration Policy 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                               |